Intel

will be moving the memory controller to the cpu......

It will be called "CSI", but won't be until '07

It will be for server chips, so we won't see it in desktop cpus till ~'08?

EETimes wrote:The CSI bus is also expected to appear in 2007 versions of Intel's x86 Xeon server CPUs, probably including the chip code-named Whitefield.

The CSI bus is optimized for low latency when used as a cache coherent processor bus in four-processor systems. However, it can also be used to link up to 16 CPUs for the high-end X86 systems built by OEMs such as IBM, NEC and Unisys. In addition, CSI will be used without cache coherency as a standard way to link north and south bridge chips in a processor core logic set

link

Conroe should be interesting as Intel has shortened the pipeline....a short pipeline is what makes AMD better for gaming etc. (games don't use large instructions!)

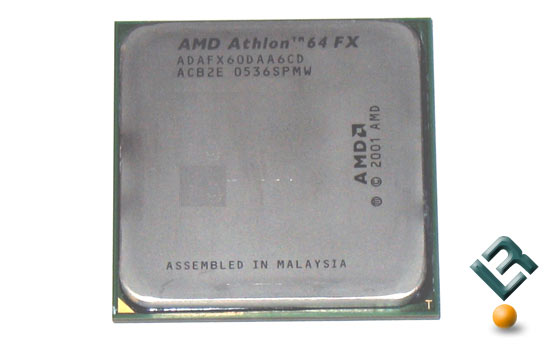

AMD have being working with memory companies and others perfecting their new ddr2 memory controller...IF they have it sorted then we should see some performance....but I can't see how more bandwith will help with higher latencies...I suspect with ddr-667, the extra MHz will be to compensate for the higher latency...

What also may happen is AMD will have to bring out a few revisions of their cpu's to gain from DDR2....if that's the case, then AM2 will have no performance benefits for the first few months...

2$